# A Continuous-Input-Current Passive-Stacked Third-Order Buck Converter Achieving 0.7W/mm<sup>2</sup> Power Density and 94% Peak Efficiency

Abdullah Abdulslam and Patrick P. Mercier University of California, San Diego, La Jolla, CA

#### **Motivation**

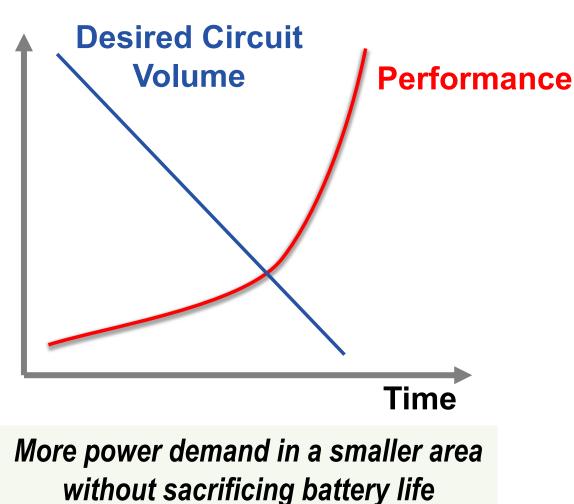

Consumer electronics are shrinking down while performance demand is increasing:

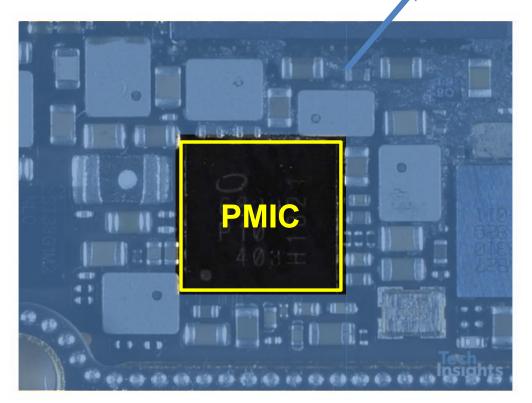

#### PCB of iPhone Xs Max\*

\*https://www.techinsights.com/

#### **Motivation**

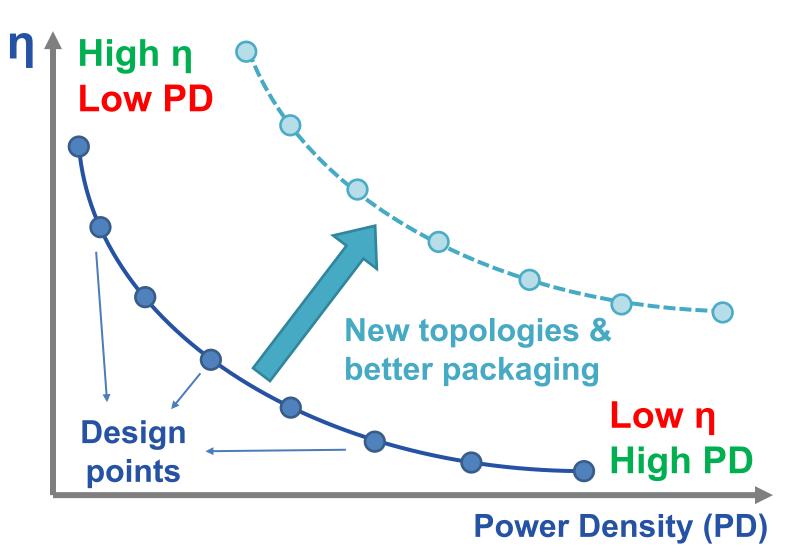

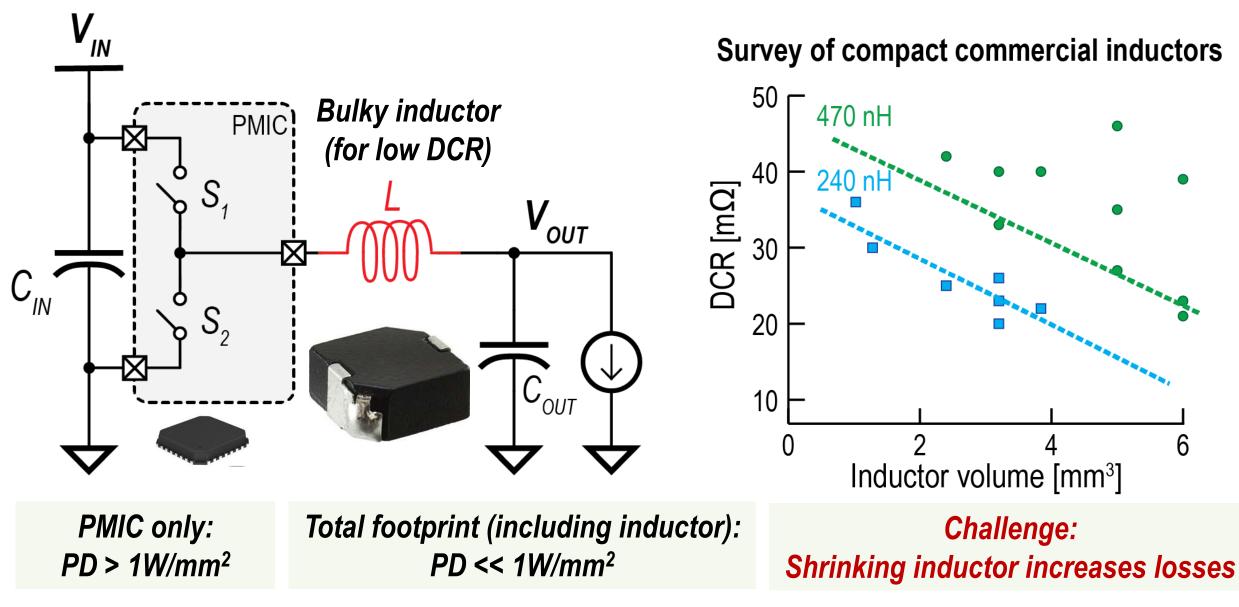

Tradeoff between efficiency and power density:

#### **Conventional Buck Converter**

## **Building Up The PS3B Converter**

Starting from a conventional buck converter:

$V_{IN}I_{IN} \approx V_{OUT}I_{OUT}$  $I_{OUT} > I_{IN}$

Inductors are placed at the highcurrent side of the converter

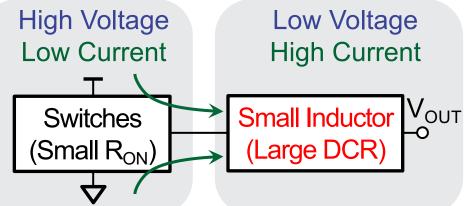

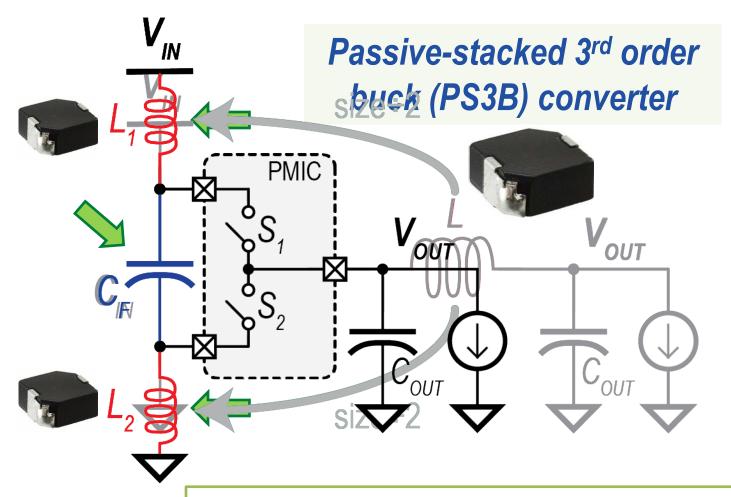

## **Building Up The PS3B Converter**

#### Moving the inductor to the input-side:

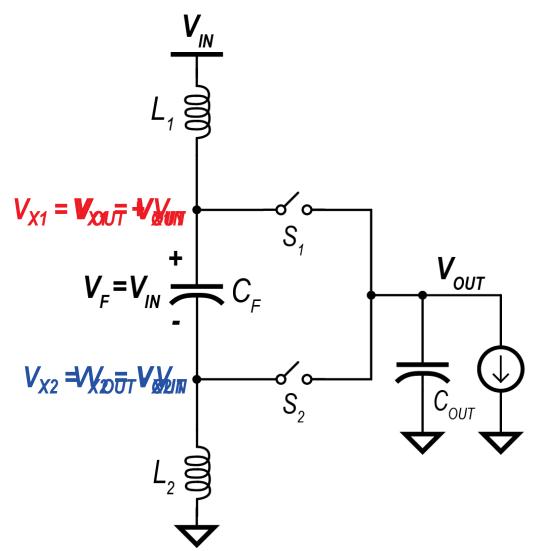

Split into two half-sized inductors and stack at input

The input capacitor is now flying

All passives are stacked at input

Inductors are placed at the low-current side of the converter

## Outline

Motivation

#### PS3B Topology

- Basic operation

- Loss-related benefits

- Noise-related benefits

- Structure-related benefits

- Converter Implementation

- Measurement Results

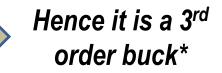

#### **Converter Basic Operation**

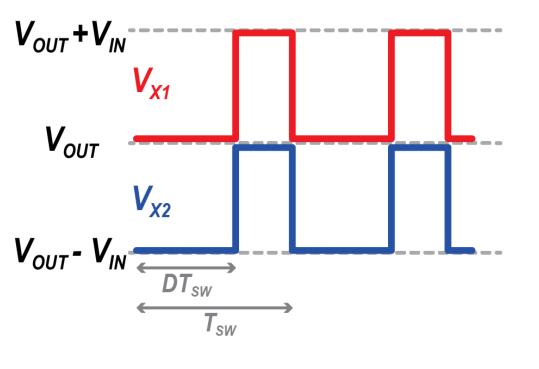

Voltage at switching nodes:

What is the relation between  $V_{IN}$  and  $V_{OUT}$ ?

#### **Converter Basic Operation**

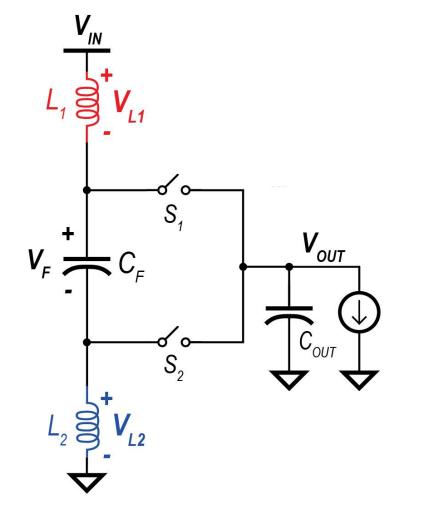

Inductor volt-second relations:

$L_{1}: (V_{IN} - V_{OUT})D + (V_{IN} - V_{F} - V_{OUT})(1-D) = 0$   $L_{2}: (V_{OUT} - V_{F})D + V_{OUT}(1-D) = 0$   $V_{F} = V_{IN}$   $V_{OUT} = DV_{IN}$

Relation between  $V_{IN}$  and  $V_{OUT}$  is the same as a buck converter

But achieved through 3 passive elements

[\*] R. Tymerski et al, INTELEC, 1986.

#### **Converter Basic Operation**

## Outline

Motivation

#### PS3B Topology

- Basic operation

- Loss-related benefits

- Noise-related benefits

- Structure-related benefits

- Converter Implementation

- Measurement Results

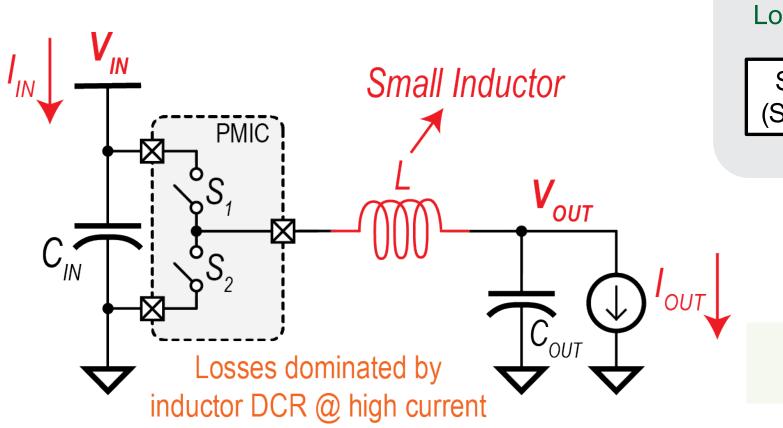

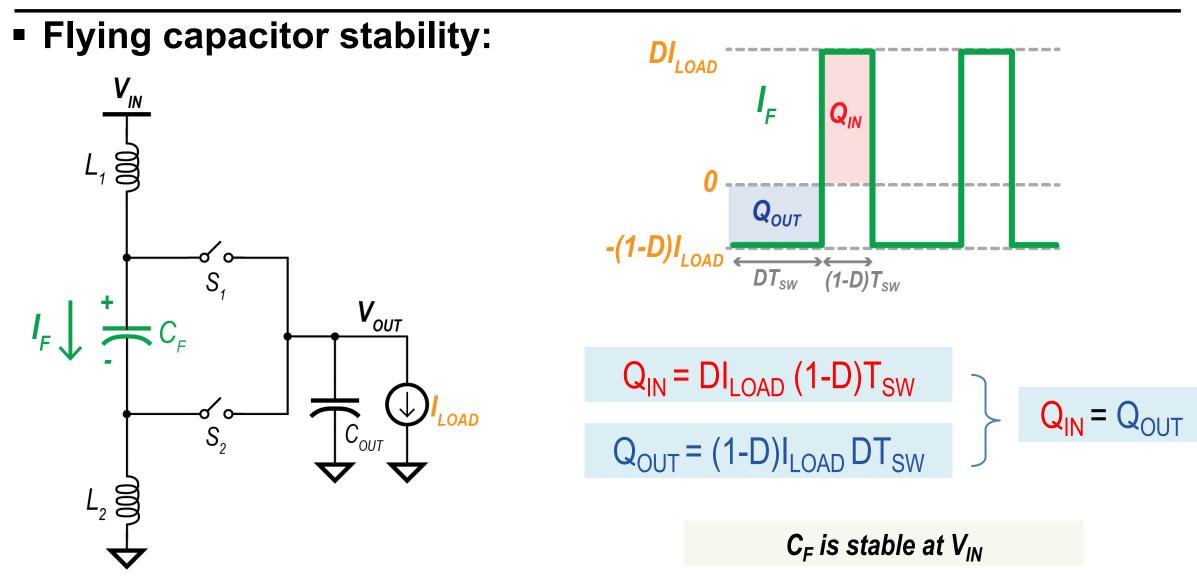

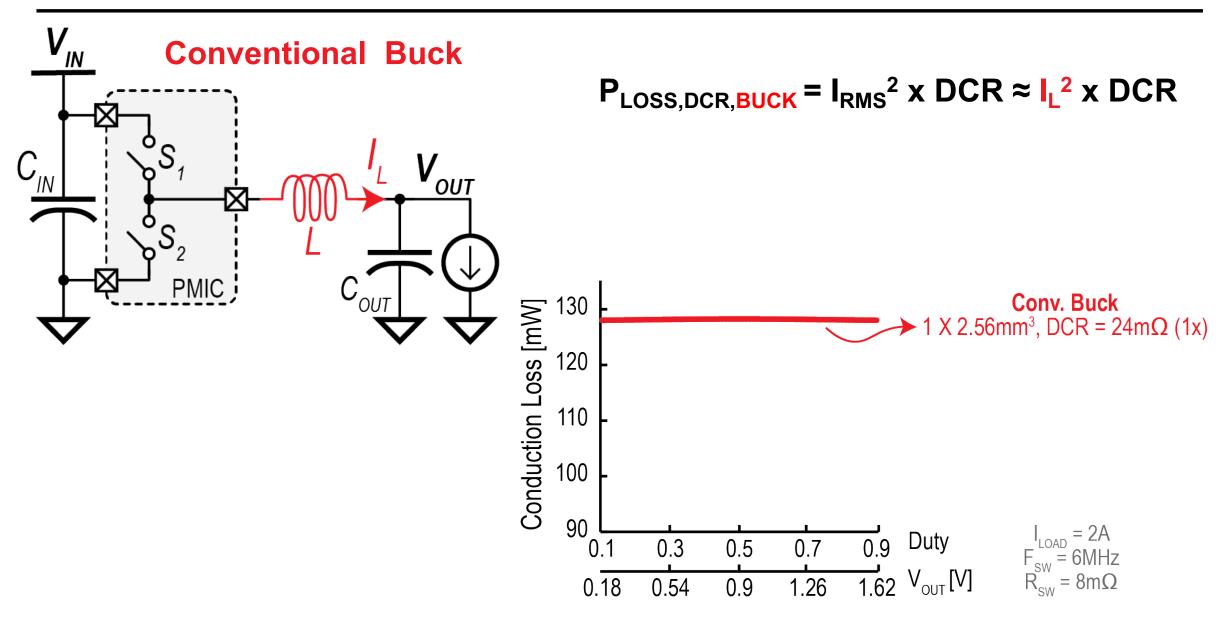

#### **Loss-Related Benefits**

#### **Loss-Related Benefits**

International Solid-State Circuits Conference

Achieving 0.7W/mm<sup>2</sup> Power Density and 94% Peak Efficiency

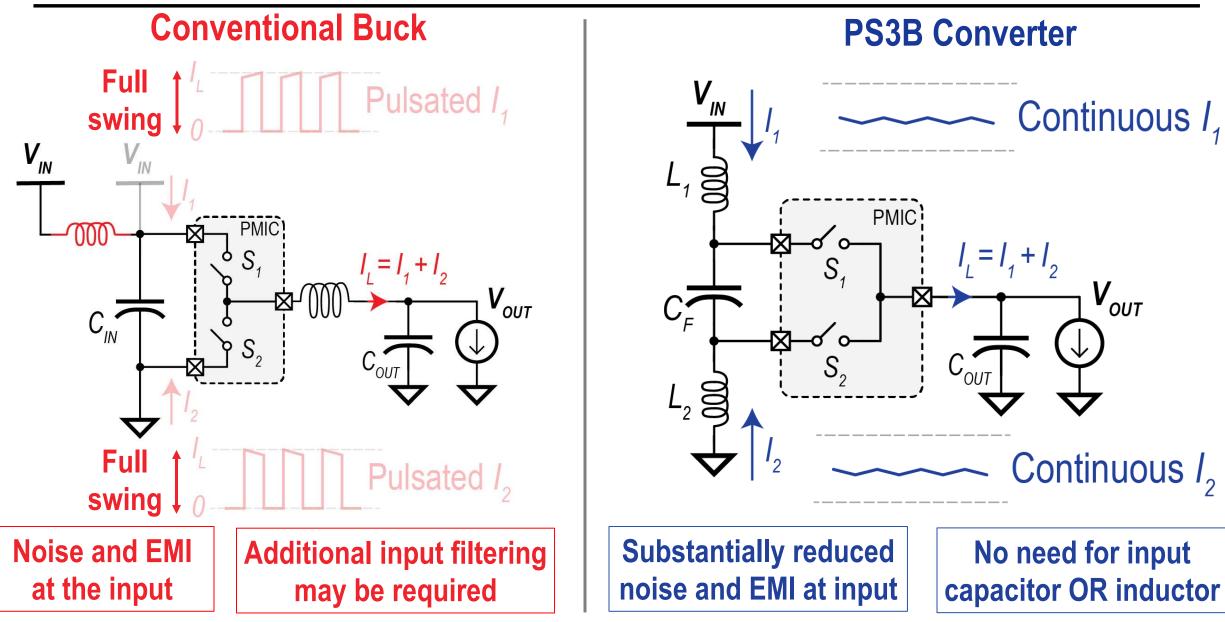

#### **Noise-Related Benefits**

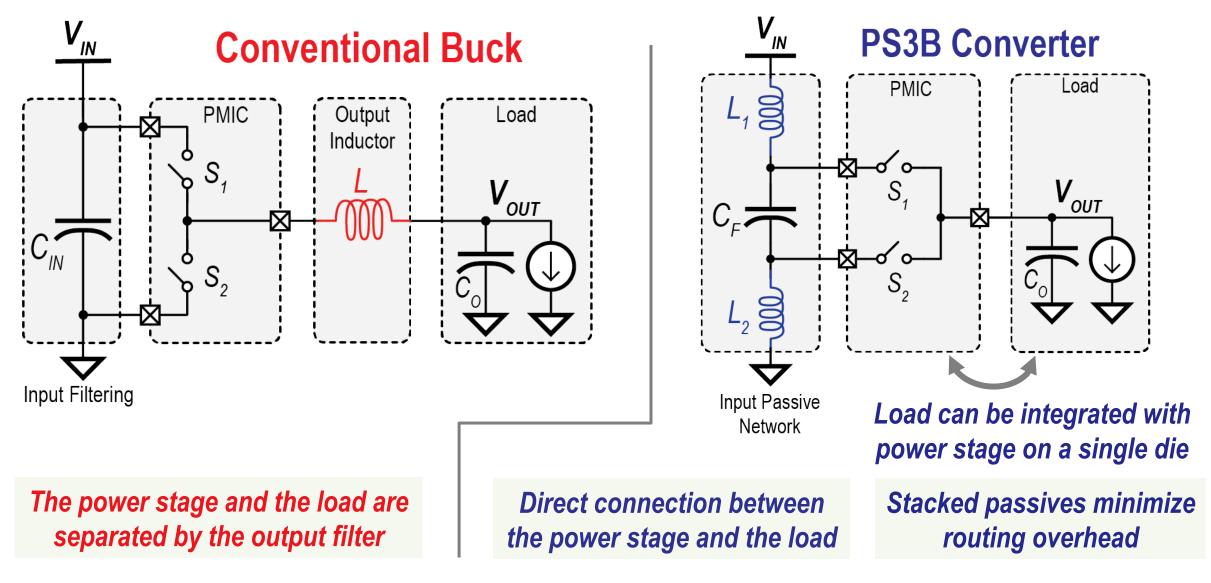

#### **Structure-Related Benefits**

## Outline

Motivation

#### PS3B Topology

- Basic operation

- Loss-related benefits

- Noise-related benefits

- Structure-related benefits

- Converter Implementation

- Measurement Results

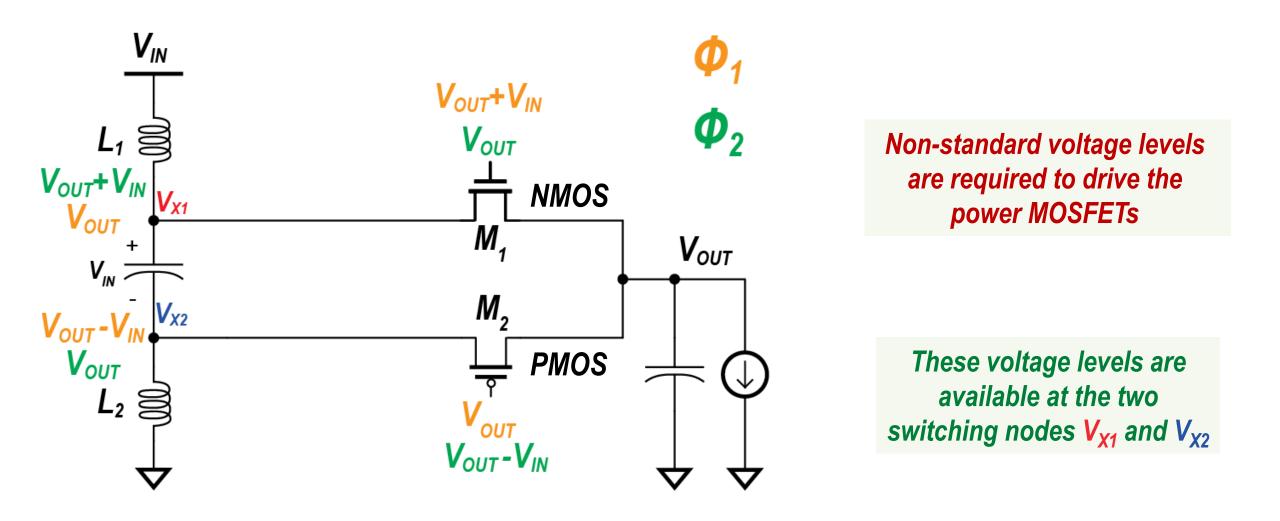

#### **Implementing Power MOSFETs**

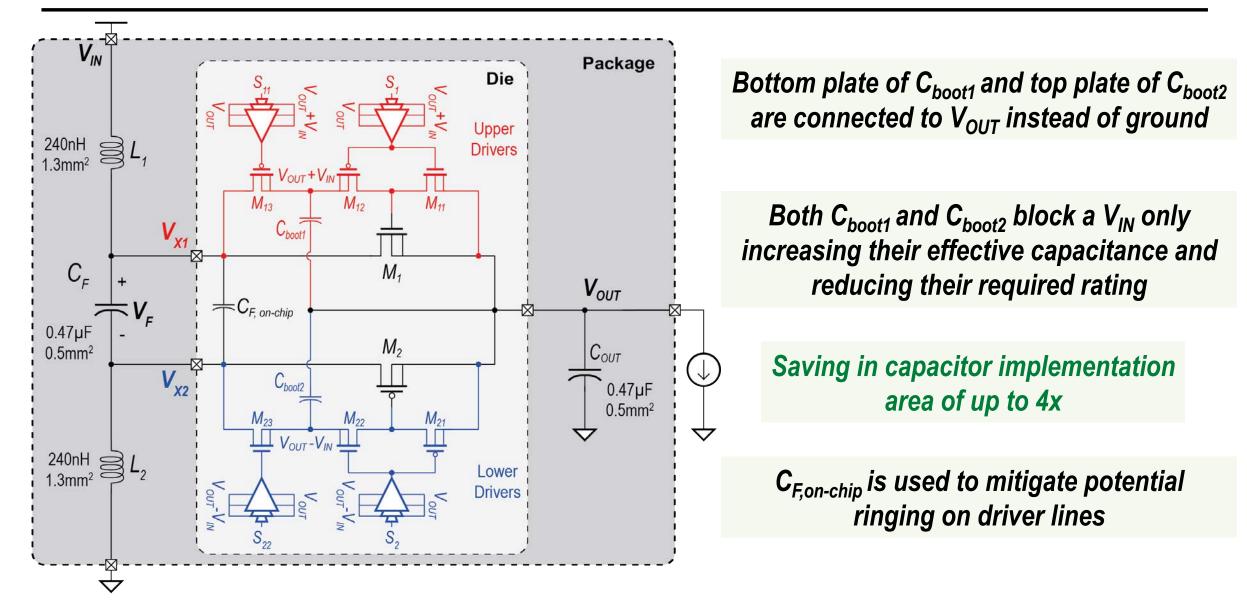

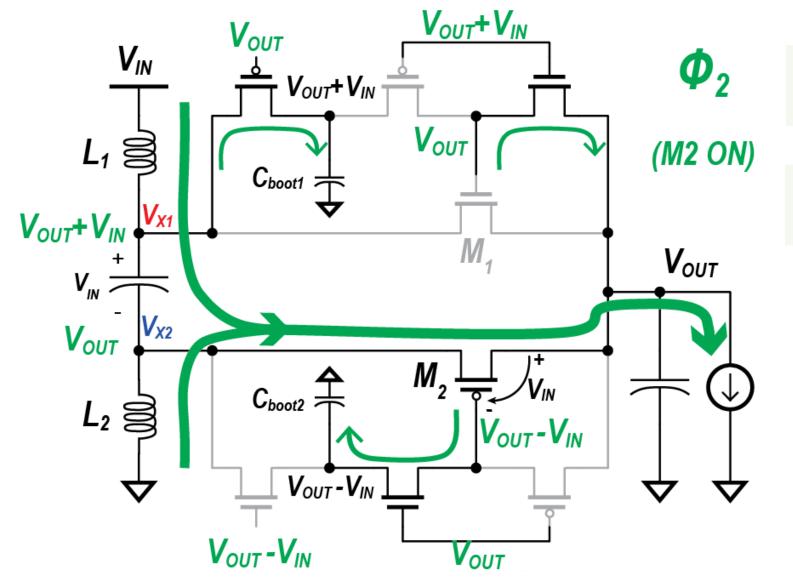

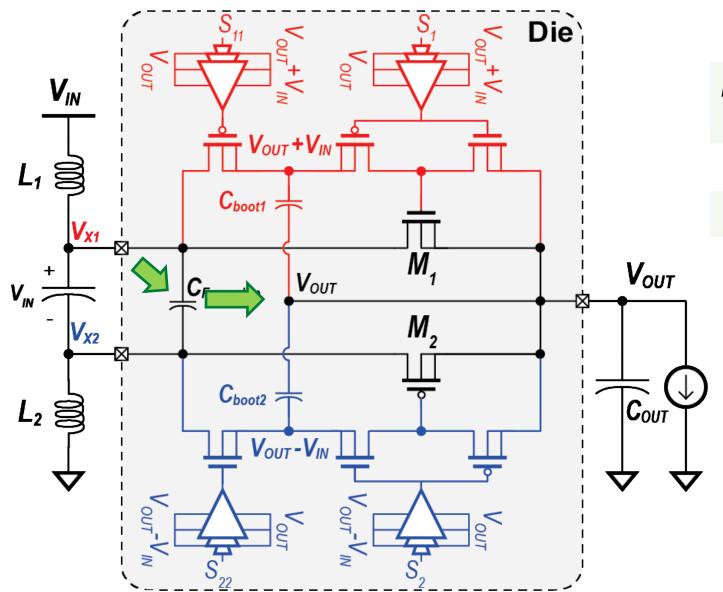

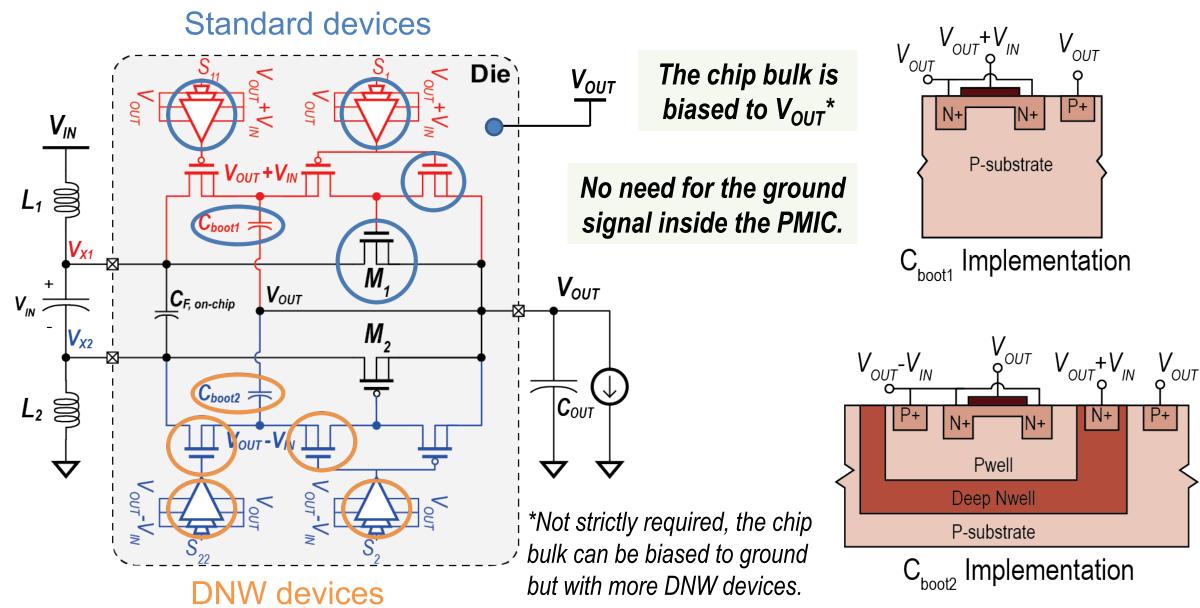

## **MOSFET Drivers Using Bootstrapping Capacitors**

```

C<sub>boot1</sub> stores the (V<sub>OUT</sub>+V<sub>IN</sub>) level

and is used to drive M1

```

C<sub>boot2</sub> stores the (V<sub>OUT</sub> -V<sub>IN</sub>) level and is used to drive M2

Power MOSFETs are driven from the internal nodes

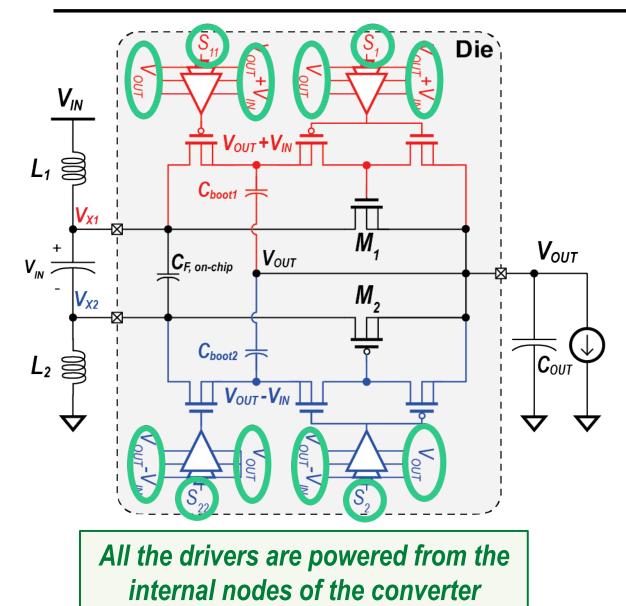

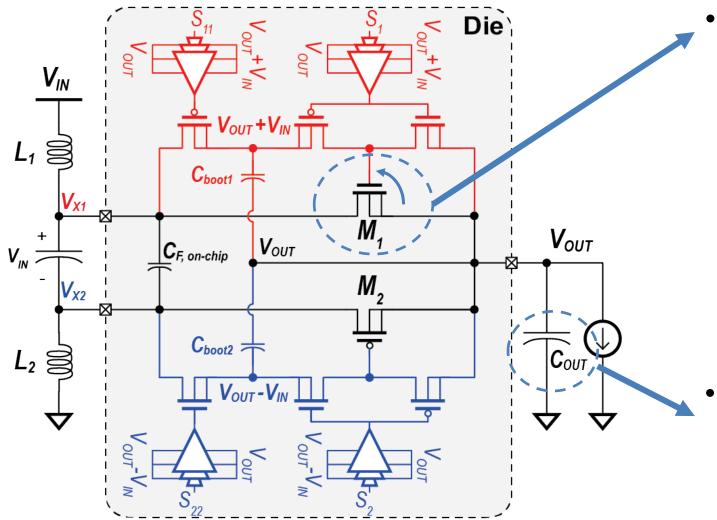

#### **Converter Full Schematic**

Bottom plate of  $C_{boot1}$  and top plate of  $C_{boot2}$ are connected to  $V_{OUT}$  instead of ground

Both C<sub>boot1</sub> and C<sub>boot2</sub> block V<sub>IN</sub> only

Up to 4x saving in capacitor implementation area

C<sub>F,on-chip</sub> is used to mitigate potential ringing on driver lines

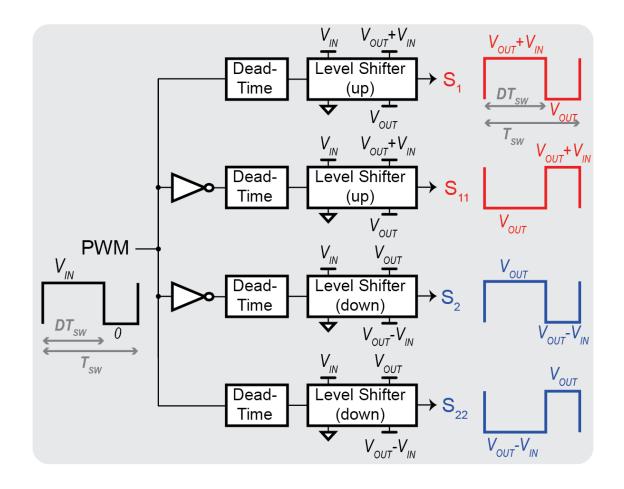

#### **Switch Drivers**

Four level-shifted control signals are generated from a single PWM signal

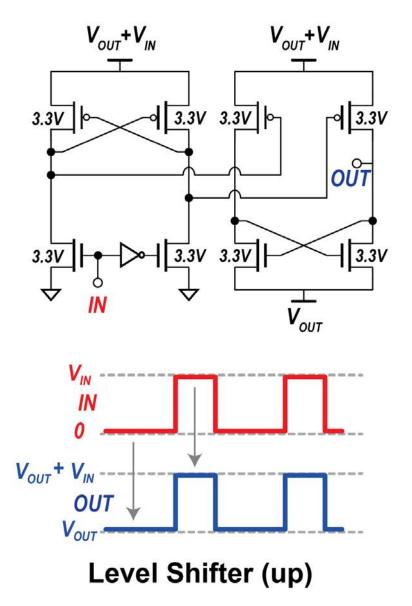

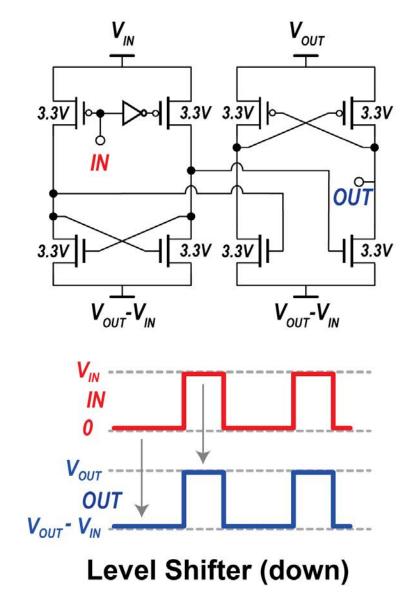

#### **Level Shifters**

No need for external supplies for level shifters

#### **PMIC Implementation**

© 2019 IEEE International Solid-State Circuits Conference

## **PMIC Implementation**

- Switching losses:

- Parasitic capacitance of both power MOSFETs experience same  $\Delta V$  as a buck converter.

- PS3B and conventional buck converter have same switching losses.

- The current ripple at the output is doubled:

- Need to use larger output capacitor.

- In this design, 0.47µF was sufficient to get output ripples <30mV.</li>

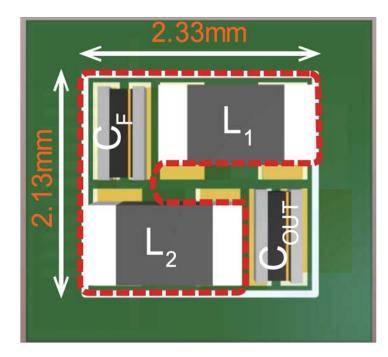

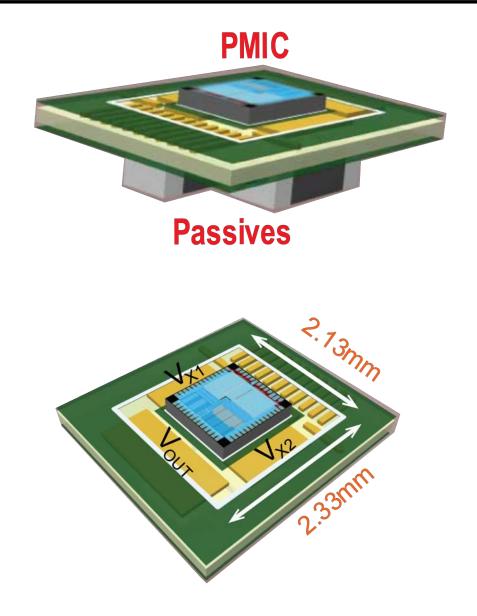

#### **Converter Packaging**

Total footprint: 5mm<sup>2</sup> including all the passives and the routing

Passives stacked at the input allows for saving in the routing area

## Outline

Motivation

#### PS3B Topology

- Basic operation

- Loss-related benefits

- Noise-related benefits

- Structure-related benefits

- Converter Implementation

- Measurement Results

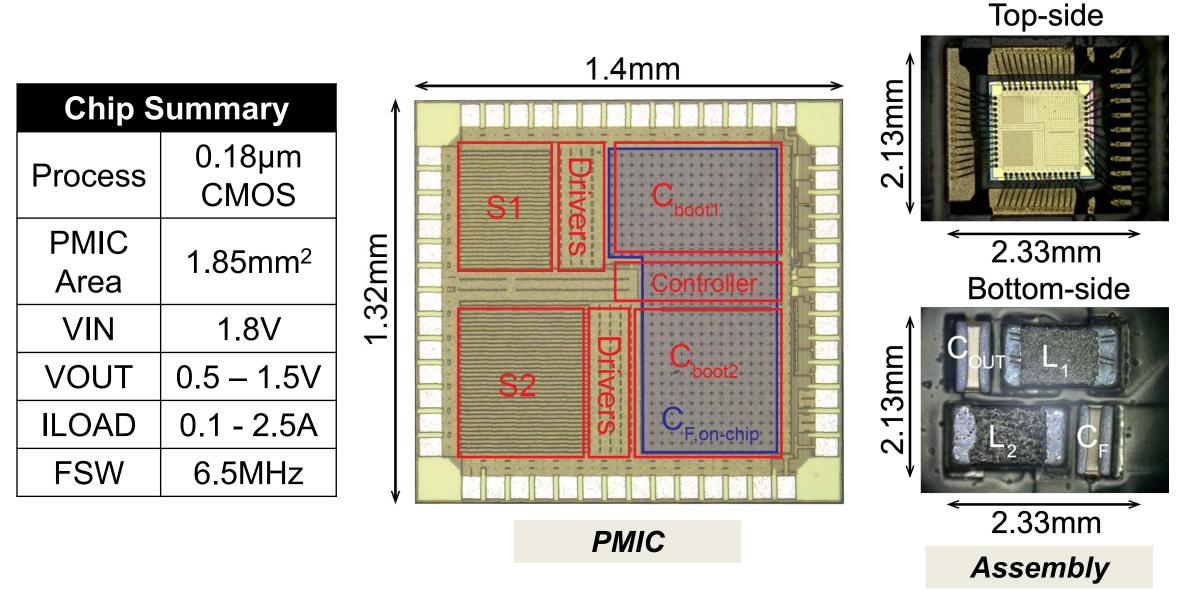

#### **Die Photo and Converter Assembly**

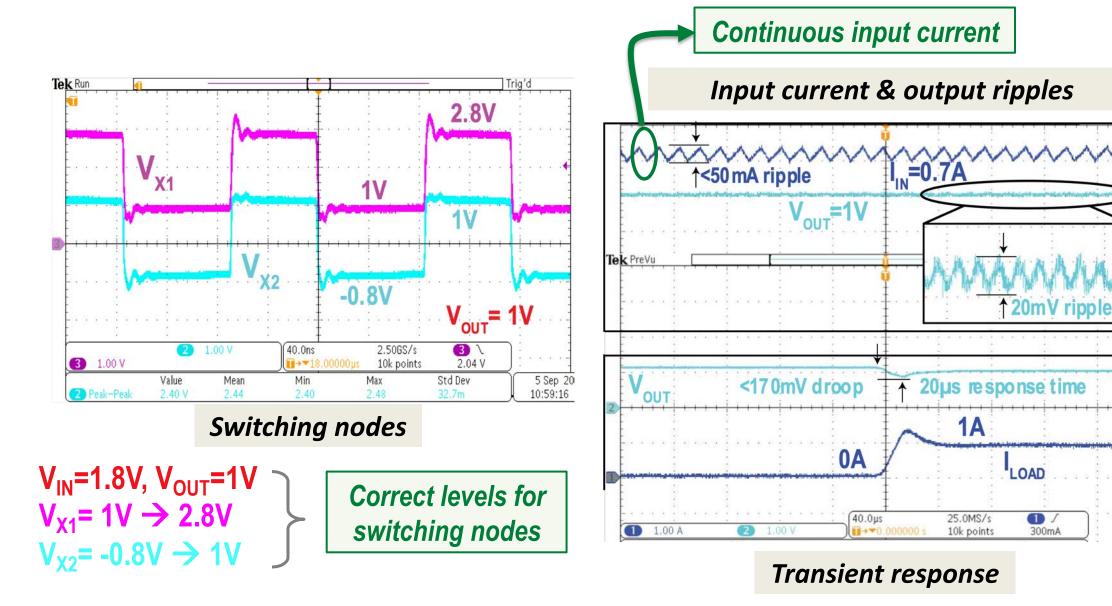

#### **Measured Waveforms**

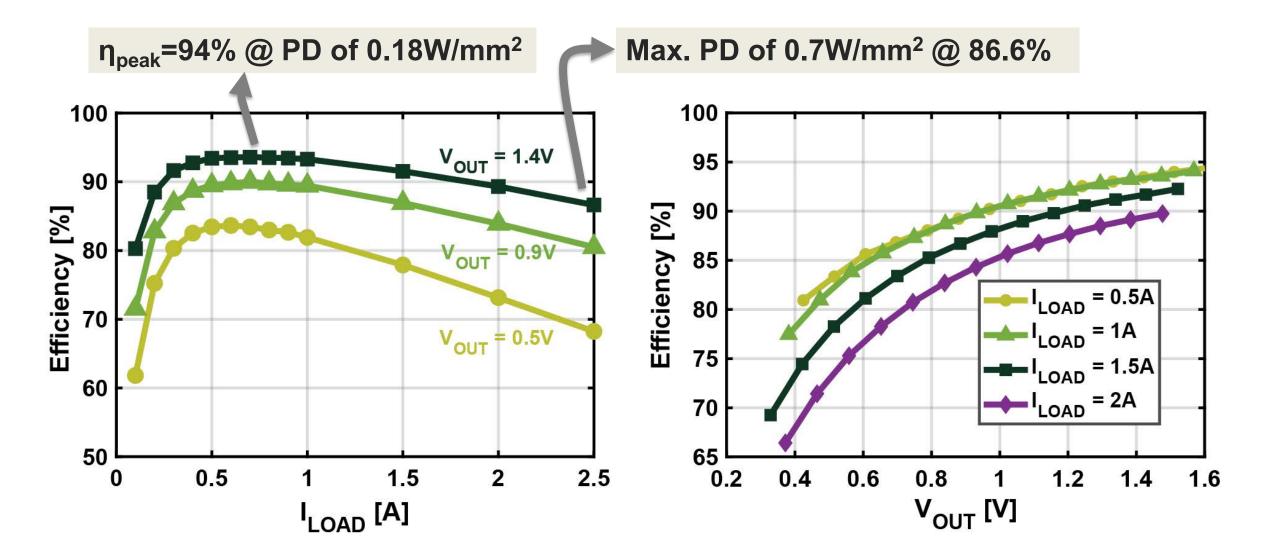

#### **Measured Efficiency**

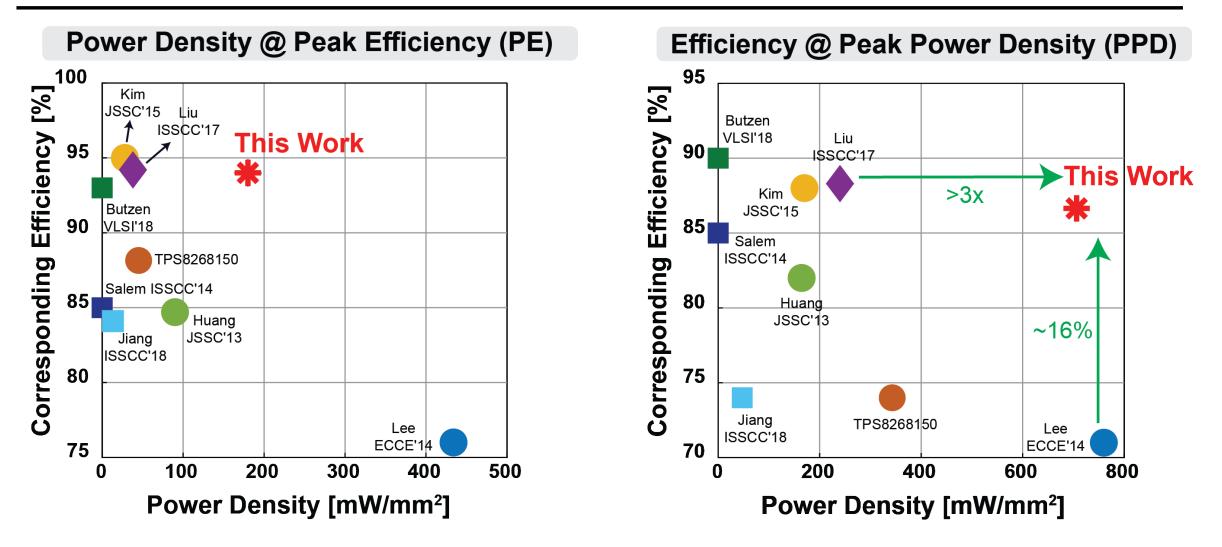

## **Power Density Comparison**

\*Only switched-capacitor or resonant converters are shown with a high number of conversion ratios to mimic a continuous conversion ratio for DVFS-enabled voltage regulation.

## **Table of Comparisons**

|                                                   | Kim JSSC'15 | Lee ISSCC'17      | Liu ISSCC'17           | Jia JSSC'18 | Jiang ISSCC'18 | TI TPS8268150 | This Work        |

|---------------------------------------------------|-------------|-------------------|------------------------|-------------|----------------|---------------|------------------|

| Тороlоду                                          | Buck        | Buck<br>(4-phase) | Hybrid<br>(Multilevel) | Buck        | SC (26 ratios) | Buck          | Hybrid<br>(PS3B) |

| Technology                                        | 65nm        | 350nm             | 65nm                   | 65nm        | 65nm           | NR            | 180nm            |

| Input Voltage [V]                                 | 1.8         | 3.3               | 3.0 - 4.5              | 1.1         | 0.22 – 2.4     | 2.3 - 5.5     | 1.8              |

| Output Voltage [V]                                | 0.6 – 1.5   | 0.3 – 2.5         | 0.3 – 1.0              | 0.3 – 0.86  | 0.85 – 1.2     | 1.5           | 0.5 – 1.5        |

| I <sub>LOAD</sub> (MAX) [A]                       | 0.6         | 6                 | 1.53                   | 0.04        | 0.08           | 1.6           | 2.5              |

| Input Current                                     | Pulsated    | Pulsated          | Pulsated               | Pulsated    | Pulsated       | Pulsated      | Continuous       |

| PMIC Area [mm <sup>2</sup> ]                      | 5           | 1.88              | 4.05                   | 0.13        | 2.42           | 6.67          | 1.85             |

| Total Footprint [mm <sup>2</sup> ]                | 5           | NR                | 6**                    | 0.13        | 2.42           | 6.67          | 5                |

| Peak Efficiency (PE)                              | 95.5%       | 88.1%             | 94.2%                  | 73%         | 84.1%          | 88%***        | 94%              |

| Power Density @<br>PE* [W/mm²]                    | 0.03***     | NR****            | 0.04**                 | NR          | 0.013          | 0.045***      | 0.18 (0.25**)    |

| Peak Power Density<br>(PPD)* [W/mm <sup>2</sup> ] | 0.17        | NR****            | 0.24                   | 0.27        | 0.034***       | 0.36***       | 0.7 (1.0**)      |

| Efficiency @ PPD                                  | 88%         | NR****            | 88.3%                  | NR          | 74%***         | 74%***        | 86.6%            |

\* Unless otherwise specified, power densities are computed with respect to the total converter footprint including the passives and routing

\*\* Computed by summing the area of the passive component footprints

\*\*\* Estimated from measurement results

\*\*\*\* The area of the passives are not reported

© 2019 IEEE International Solid-State Circuits Conference

## Summary

- A 3<sup>rd</sup> order buck is introduced:

- Reduced conduction loss.

- Continuous input current.

- Small passives stacked at the input.

- Achieves a high power density amongst prior-art converters that operate @ >85% efficiency with continuous conversion ratios across SoC-compatible voltage ranges.

- Achieves comparable peak efficiency (94%) @ >4x higher power density than prior-art.

- Has a unique feature of continuous input current, which would help minimize the area needed for on-board filtering.

Acknowledgement: pSemi Corporation

## **Backup slides**

#### **Converter Full Schematic**